Chiapas ha sido uno de los estados que ha crecido exponencialmente en temas de investigación científica, prueba de ello es el diseño de un Microprocesador PLC basado en FPGA -hasta donde se sabe es el primer diseño desarrollado en Chiapas-. El microprocesador fue desarrollado por Manuel de Jesús Cancino Escobar, egresado de la Maestría en Ciencias de la Ingeniería Mecatrónica del Tecnológico Nacional de México campus Tuxtla Gutiérrez bajo la dirección del Dr. Carlos A Hernandez Gutierrez profesor investigador del instituto.

Cancino Escobar, dio a conocer que con el Microprocesador PLC basado en FPGA de baja latencia para automatización industrial conforme a IEC-61131-3, se da paso a desarrollar nuevas tecnologías en Chiapas ya que existe un paradigma que asegura que en Chiapas es complicado desarrollar tecnología relevante.

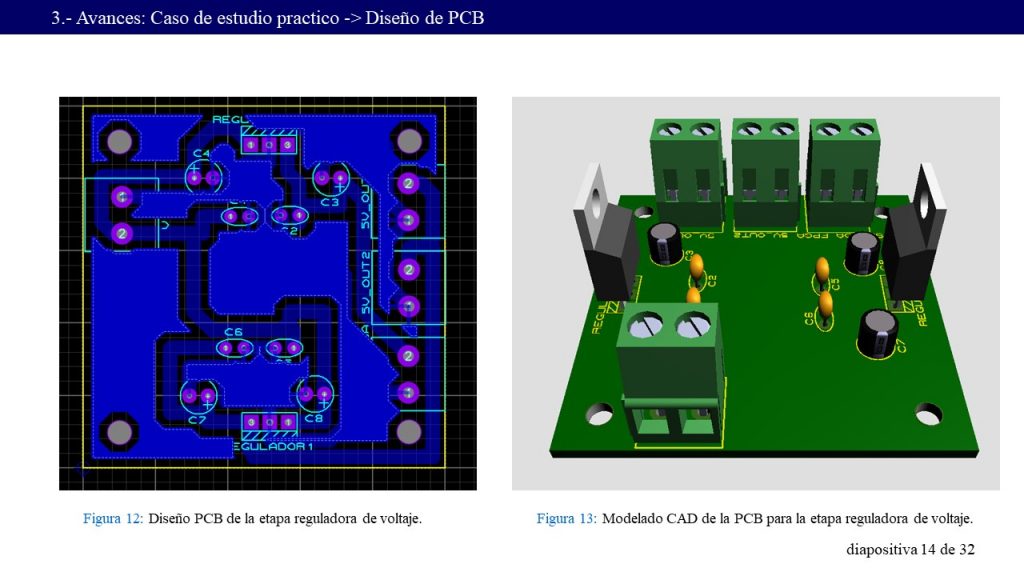

“Este estudio presenta el diseño y la implementación de un microprocesador PLC que cumple con el estándar IEC-61131-3, ejecutado en un FPGA Cyclone V utilizando una placa de desarrollo DE10-NANO, con la creación de este microprocesador damos paso a que nuevas generaciones del instituto puedan desarrollarlo continuamente, el desarrollo de este microprocesador fue hecho en una FPGA con una computadora y con el ingenio del grupo de semiconductores”.

Asimismo dio a conocer que el pasado 19 de abril de 2024, este proyecto fue publicado en la revista Arabian Journal for Science and Engineering como artículo de investigación en Ingeniería eléctronica.

“Nuestro microprocesador optimiza la unidad central de procesamiento al agilizar la ruta de datos, logrando un notable tiempo de respuesta simulado de aproximadamente 60 ns, equivalente a tres ciclos de reloj a una frecuencia de 50 MHz para operaciones booleanas. Para corroborar nuestro enfoque, realizamos experimentos prácticos utilizando una estación transportadora FESTO, empleando relés como actuadores e incorporando sensores ópticos e inductivos. Los resultados subrayan la viabilidad de nuestro enfoque propuesto y sirven como validación práctica de su eficacia”.

Cabe señalar que este trabajo presenta una vía prometedora para el desarrollo de PLC rentables que emplean variantes de FPGA SoC. Además, una comparación exhaustiva de los tiempos de ejecución con otras arquitecturas informadas anteriormente.

El microprocesador supera incluso a los PLC más establecidos como el S7-312, con reducciones sustanciales en los tiempos de ejecución del 94,54% para operaciones de punto flotante, del 71,42 al 93,33% para operaciones de palabras y hasta el 78,57% para operaciones de bits.

“Ciencia y Tecnología con Sentido Humano”

Departamento de Comunicación y Difusión

TecNM campus Tuxtla Gutiérrez